|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <p><b>1. Systemebene</b><br/>Die Frequenzsynthese ist ein zentraler Teil in modernen Telekommunikationssystemen.</p> <p>Send- und Empfangsschaltung für den 2.4 GHz Bereich</p> <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 3</p>                                                                                                                                                                                                                                                                                                                           | <p>1. Einordnung des Arbeitsgebietes auf der Systemebene.</p> <p>PLL Schaltungen stellen einen zentralen Schaltungsblock in Transceivern dar.</p> <p>Die Schaltungen mit dem größten Leistungsbedarf sind gegenwärtig der HF-Leistungsverstärker, der LNA und die Frequenzsynthese.</p> <p>Ein geringerer Leistungsbedarf dieser Schaltungen unter Garantie der von den Standards (GSM, DECT) geforderten Betriebswerte kann die Batterielebensdauer mobiler Systeme deutlich vergrößern.</p> | S. 03-5   |

| <p><b>2. Subsystem CMOS-PLL</b><br/>Nahezu 100% der gesamten Betriebsergie werden in VCO und Prescaler umgesetzt.</p> <p>Niederfrequenter Teil   Hochfrequenter Teil</p> <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 4</p>                                                                                                                                                                                                                                                                                                                                  | <p>2. Analyse des Leistungsverbrauches und Beschreibung des Subsystem einer PLL Schaltung.</p> <p>Im hochfrequenten Teil der Schaltung wird nahezu die gesamte Verlustleistung einer PLL umgesetzt.</p> <p>Je nach gefordertem Standard benötigt der Frequenzteiler ca. 75% bis 95% der Gesamtverlustleistung einer solchen PLL Schaltung.</p>                                                                                                                                                | S. 09 ff. |

| <p><b>3. Frequenzteiler</b><br/>3.1. Architekturen<br/>Der Verteiler eines Frequenzteilers benötigt ca. 80% bis 95% der gesamten Betriebsernergie.</p> <p>Vorteile Basis: <math>f_{out} = f_{in} \cdot N</math><br/>Kondensator: <math>f_{out} = f_{in} \cdot N^2</math>, <math>n \in G</math></p> <p>Dual-Modulus-Verteiler: <math>f_{out} = (N+1) \cdot f_{in}</math><br/>Schleifzähler: <math>f_{out} = P \cdot f_{in}</math><br/>Kondensator: <math>f_{out} = (N \cdot P + S) \cdot f_{in}</math></p> <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 5</p> | <p>3. Erläuterung gebräuchlicher Architekturen von Frequenzteilern.</p> <p>Auch hier benötigt der Hochfrequenzverteiler den Löwenanteil der gesamten Verlustleistung.</p> <p>Moderne Systeme nutzen Dual-Mode Frequenzteiler in einer Integer-N Architektur.</p>                                                                                                                                                                                                                              | S. 30 ff. |

|                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

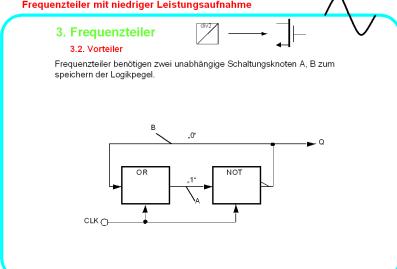

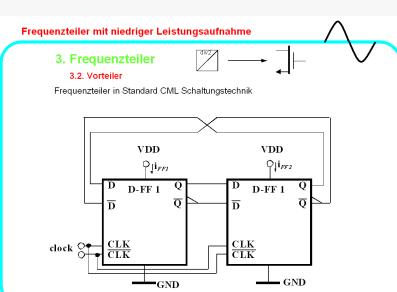

|  <p><b>Frequenzteiler mit niedriger Leistungsaufnahme</b><br/>3. Frequenzteiler<br/>3.2. Vorteile<br/>Frequenzteiler benötigen zwei unabhängige Schaltungsknoten A, B zum speichern der Logikpegel.</p> <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 6</p> | <p><b>4. Zur Theorie der Frequenzteilung.</b></p> <p>Darstellung des Grundprinzips digitaler binärer Frequenzteiler.</p> <p>Ein Eingangstaktsignal steuert die wechselseitige Abspeicherung einer logischen '1' und '0' auf zwei Schaltungsknoten in einer Ringschaltung. Damit entsteht an beiden Schaltungsknoten ein Signal der halben Takteingangs frequenz.</p>                                                                                                                                                                                                        | <p>S. 36</p>    |

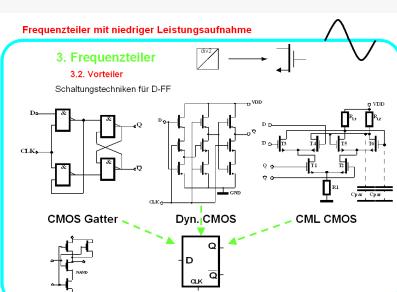

|  <p><b>Frequenzteiler mit niedriger Leistungsaufnahme</b><br/>3. Frequenzteiler<br/>3.2. Vorteile<br/>Schaltungstechniken für D-FF</p> <p>CMOS Gatter<br/>Dyn. CMOS<br/>CML CMOS</p> <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 7</p>                    | <p><b>5. Betrachtung möglicher Schaltungstechniken.</b></p> <p>Drei grundsätzliche Schaltungstechniken werden vorgestellt. Jede dieser Techniken hat Vor- und Nachteile sowie fundamentale Begrenzungen bezüglich Arbeitsfrequenzen, Verlustleistungen, Signalpegel, thermischer Stabilitäten sowie Störfestigkeit.</p> <p>Das Delay-Flip-Flop, D-FF, ist die Basis von digitalen Frequenzteilern.</p>                                                                                                                                                                      | <p>S. 36-42</p> |

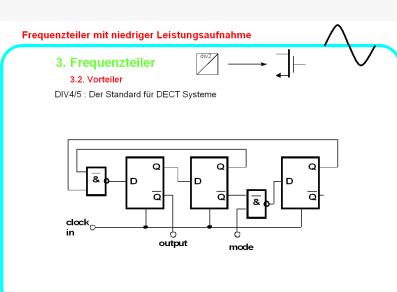

|  <p><b>Frequenzteiler mit niedriger Leistungsaufnahme</b><br/>3. Frequenzteiler<br/>3.2. Vorteile<br/>DIV4/5 : Der Standard für DECT Systeme</p> <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 8</p>                                                       | <p><b>6. Aufbau von Standard Frequenzteilern.</b></p> <p>Standardfrequenzteiler sind aus Binärteilern mit im Signalpfad befindlichen Logikschaltungen aufgebaut.</p> <p>Die Logikschaltungen begrenzen die erreichbare Schaltfrequenz, da damit zusätzliche Verzögerungszeiten auftreten.</p> <p>In einer CMOS Technologie wird die erreichbare Frequenz durch Logikblöcke im Teillerring etwa halbiert.</p>                                                                                                                                                                | <p>S. 31</p>    |

|  <p><b>Frequenzteiler mit niedriger Leistungsaufnahme</b><br/>3. Frequenzteiler<br/>3.2. Vorteile<br/>Frequenzteiler in Standard CML Schaltungstechnik</p> <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 9</p>                                            | <p><b>7. Aufbau von Standard Frequenzteilern in CML Schaltungstechnik.</b></p> <p>Differentielle Signale sind unempfindlicher gegen Störungen und ermöglichen eine sehr einfache Signalinversion. Die Schaltungen sind auf Grund des Arbeitspunktstromes sehr empfindlich und ermöglichen damit kleine nutzbare Signaleingangsspegel.</p> <p>Sie besitzen eine wenig frequenzabhängige Verlustleistung und können mit temperaturstabilisierten Stromquellen ausgestattet werden. Der Arbeitspunktstrom bestimmt die erreichbare Frequenz und die Gesamtverlustleistung.</p> | <p>S. 41 ff</p> |

|                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

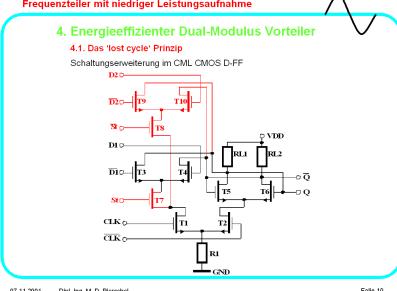

|  <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 10</p>   | <h3>8. Neuartige Schaltungserweiterung in CML D-FF's.</h3> <p>Die Schaltung eines Standard CML D-FF wurde modifiziert. Ein weiteres Eingangstransistorpaar und die zugehörigen Umschalttransistoren ergänzen die Schaltung (rot dargestellt). Damit sind bei nur unwesentlich abfallender Leistungsfähigkeit zusätzliche logische Funktionen realisierbar. Insbesondere kann jetzt zwischen den beiden integrierten Eingängen umgeschaltet werden, wobei dann der jeweils andere Eingang ungenutzt bleibt.</p> | S. 45                  |

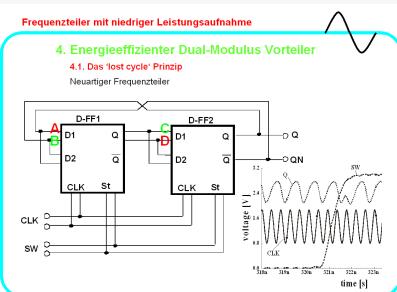

|  <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 11</p>   | <h3>9. Neuartiger Frequenzteiler unter Verwendung des modifizierten CML D-FF's.</h3> <p>Die Funktion des modifizierten Johnson-Teilerringes insbesondere beim Umschalten der Eingänge wird erläutert. Die Schaltung ermöglicht eine Division des Eingangssignals durch 2 und bietet zusätzlich die Möglichkeit einzelne Eingangstaktperioden auszublenden.</p>                                                                                                                                                 | S. 47 ff. und S. 51-56 |

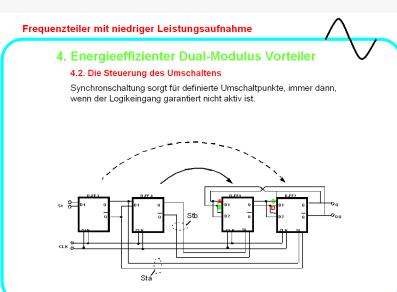

|  <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 12</p> | <h3>10. Die Synchronisation der Umschaltsignale zum HF-Eingangstaktsignal.</h3> <p>Damit können fehlerhafte Schaltsignale sicher verhindert werden. Die zusätzlich erforderlichen Synchron D-FF benötigen auch eine zusätzliche Verlustleistung.</p>                                                                                                                                                                                                                                                           | S. 50                  |

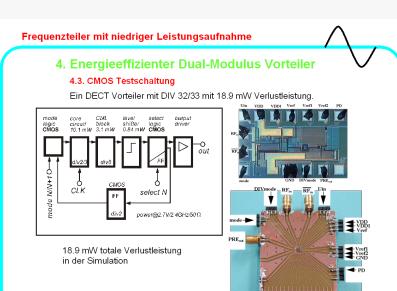

|  <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 13</p> | <h3>11. Die CMOS Testschaltung (0.4µm TSMC CMOS).</h3> <p>Erläuterung der Schaltungsblöcke, Chip und Platinenlayout.</p> <p>Verlustleistung innerhalb der Schaltung bei 2.4 GHz:<br/>     7mW im Synchronblock<br/>     3.1 mW im Verteiler div2/3<br/>     3.1 mW im CML div8 Block<br/>     0.84 mW in Pegelwandlern CML-&gt;CMOS Logik</p>                                                                                                                                                                  | S. 60 ff.              |

|                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                |                  |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

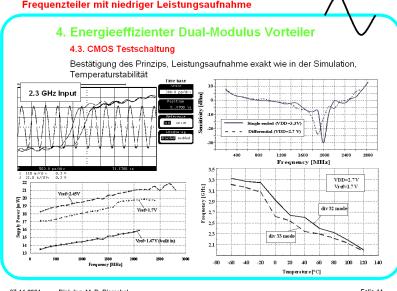

|  <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 14</p>   | <p><b>12. Messungen an der Testschaltung.</b></p> <p>Die Messungen bestätigen die Funktion des Grundprinzips auch bei hohen Frequenzen.</p> <p>Die Verlustleistung liegt in dem aus der Simulation erwarteten Bereich. Die Schaltung besitzt eine gute Eingangsempfindlichkeit und die erwartete Temperaturabhängigkeit bis 120 °C (keine kompensierten Quellen).</p>                                          | <p>S. 65 ff.</p> |

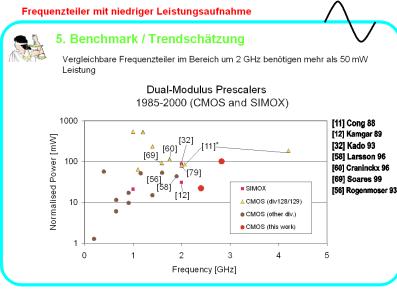

|  <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 15</p>   | <p><b>13. Der Vergleich mit anderen CMOS Frequenzteilern.</b></p> <p>Vergleichbare Frequenzteiler im Bereich um 2 GHz mit div128/129 benötigen mehr als 50 mW Verlustleistung.</p>                                                                                                                                                                                                                             | <p>S. 70</p>     |

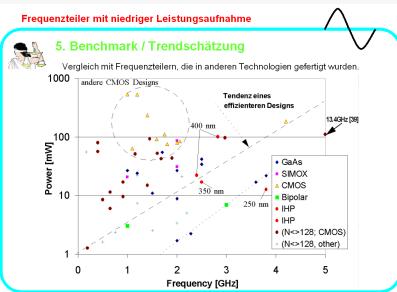

|  <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 16</p> | <p><b>14. Der Vergleich mit Frequenzteilern in anderen Technologien (Binäre und Dual-Mode Frequenzteiler).</b></p> <p>Effizientere Designs zeigen die Tendenz in den rechten unteren Bereich der Grafik zu gelangen.</p> <p>Die neuartigen CMOS Schaltungen erreichen die eingezeichnete Frequenz-Leistungsgrenze. In dem dahinter folgenden Bereich sind GaAs und einzelne Bipolartechnologien vertreten.</p> | <p>S. 71</p>     |

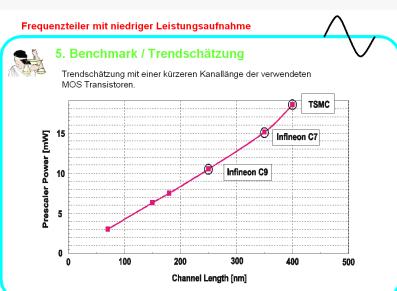

|  <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 17</p> | <p><b>15. Trendschätzung der Verlustleistungsaufnahme als Funktion der Transistorkanallänge.</b></p> <p>Moderne CMOS Technologien mit Kanallängen unter 180 nm lassen monolithisch integrierte PLL-Schaltungen mit weniger als 8 mW Gesamtleistungsaufnahme erwarten.</p>                                                                                                                                      | <p>S. 73</p>     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

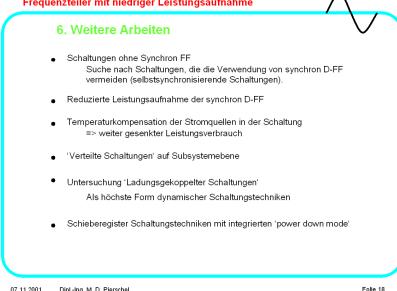

|  <p><b>Frequenzteiler mit niedriger Leistungsaufnahme</b></p> <p><b>6. Weitere Arbeiten</b></p> <ul style="list-style-type: none"> <li>Schaltungen ohne Synchron D-FF<br/>Suche nach Schaltungen, die die Verwendung von synchron D-FF vermeiden (selbstsynchroisierende Schaltungen).</li> <li>Reduzierte Leistungsaufnahme der synchron D-FF</li> <li>Temperaturkompensation der Stromquellen in der Schaltung<br/>=&gt; weiter gesenkter Leistungsverbrauch</li> <li>'Verteilte Schaltungen' auf Subsystemebene</li> <li>Untersuchung 'Ladungskopplter Schaltungen'<br/>Als höchste Form dynamischer Schaltungstechniken</li> <li>Schieberegister Schaltungstechniken mit integrierten 'power down mode'</li> </ul> <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 18</p> | <p><b>16. Weitere Arbeiten.</b></p> <p>Vorschläge für weiterführende Arbeiten.</p>                                                                                                                                                                                                                                                                                                                                                                                             | <p>S. 75 ff.</p>          |

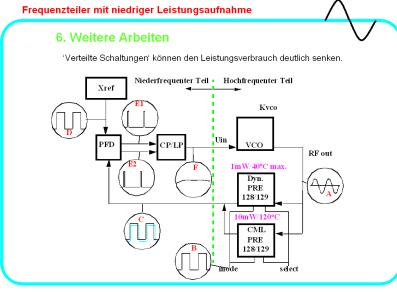

|  <p><b>Frequenzteiler mit niedriger Leistungsaufnahme</b></p> <p><b>6. Weitere Arbeiten</b></p> <p>'Verteilte Schaltungen' können den Leistungsverbrauch deutlich senken.</p> <p>Block diagram showing the architecture of a frequency divider. It includes a VCO, DCO, PLL, and various logic blocks. A 'Low Power Mode' section is highlighted, showing components like a CML driver and a CMOS inverter.</p> <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 19</p>                                                                                                                                                                                                                                                                                                        | <p><b>17. Durch Veränderung an der Architektur auf der Teilsystemebene können beträchtliche Verlustleistungsanteile einer PLL minimiert werden.</b></p> <p>'Verteilte' Schaltungen ermöglichen ein Design welches einerseits die Systemanforderungen in allen Betriebsbereichen sicherstellt, andererseits die Energieeffizienz unterstützt.</p>                                                                                                                               | <p>S. 76</p>              |

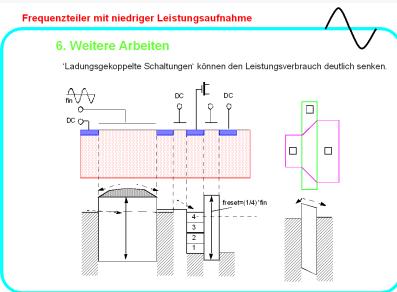

|  <p><b>Frequenzteiler mit niedriger Leistungsaufnahme</b></p> <p><b>6. Weitere Arbeiten</b></p> <p>'Ladungskopplte Schaltungen' können den Leistungsverbrauch deutlich senken.</p> <p>Diagram showing a cross-section of a CMOS switch and a charge-packet switch. The charge-packet switch uses discrete charge packets instead of a continuous current.</p> <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 20</p>                                                                                                                                                                                                                                                                                                                                                        | <p><b>18. Dynamisch betriebene Schaltungen besitzen noch Reserven.</b></p> <p>Im Idealfall werden statt eines Stromes nur noch diskrete sogenannte 'Ladungspakete' genutzt.</p> <p>Die CMOS Technologie bietet Möglichkeiten für die Implementierung derartiger Techniken.</p>                                                                                                                                                                                                 | <p>S. 77</p>              |

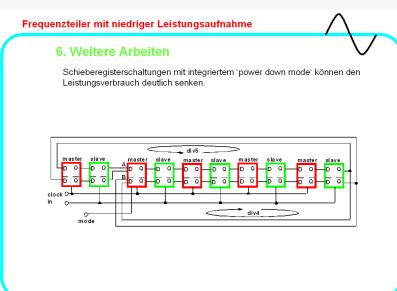

|  <p><b>Frequenzteiler mit niedriger Leistungsaufnahme</b></p> <p><b>6. Weitere Arbeiten</b></p> <p>Schieberegisterschaltungen mit integriertem 'power down mode' können den Leistungsverbrauch deutlich senken.</p> <p>Diagram showing a shunt register ring architecture for frequency division. It illustrates how multiple shunt registers can be used to reduce power consumption.</p> <p>07.11.2001 Dipl.-Ing. M. D. Pierschel Folie 21</p>                                                                                                                                                                                                                                                                                                                           | <p><b>19. Auch Schieberegisterringe bieten möglicherweise weiter interessante Ansätze für energieeffiziente Multi-Mode Frequenzteiler.</b></p> <p>Die entsprechenden Ansätze wurden aus Zeitgründen nicht weiter verfolgt. Diese Schaltungstechnik stellt jedoch noch ein erhebliches Potential für energieeinsparende Schaltungen bereit. Insbesondere könnte mit den hier vorgestellten modifizierten D-FF das Problem der erforderlichen Initialisierung gelöst werden.</p> | <p>S. 43-44 und S. 77</p> |

**Frequenzteiler mit niedriger Leistungsaufnahme**

Ich bedanke mich bei :

Herrn Prof. Dr. A. Ourmazd

Herrn Prof. Dr. P. Weger

Herrn Dr. H. Gustat

Herrn Dr. W. Winkler

Herrn Prof. Dr. B. Falter

Sowie allen Mitarbeitern des IHP und der TU Cottbus

für die Hinweise, Ratschläge, Hilfe und Unterstützung.